Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Select Language

introduction

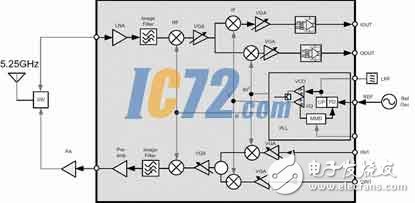

Driven by the current communications market, communication technology is advancing rapidly. Hand-held wireless communication terminals have become one of the hot applications. Therefore, monolithically integrated RF transceiver systems are receiving increasing attention. Typical RF transceiving systems include low noise amplifiers (LNAs), mixers, filters, variable gain amplifiers, and frequency synthesizers that provide the necessary local oscillators, as shown in Figure 1. For circuit systems operating in RF environments, such as 2.4G or 5G WLAN applications, the system must include a small signal noise sensitive circuit for the RF front end, a module with high linearity for the baseband low frequency large signal, and a high current PA at the transmitter. Modules, digital blocks in a PLL frequency synthesizer, and nonlinear circuits such as VCOs. Numerous circuit elements and their rich features necessarily require a rich and powerful design platform in the design process of this system. After a comprehensive comparison, this article selected the Cadence Virtuoso full custom IC design tool.

Figure 1 Typical RF Transceiver System

Virtuoso is Cadence's professional software for analog/digital hybrid circuit simulation and RF circuit simulation. Based on this platform, Cadence also developed new technologies for RF design, including RF extraction technology and two new design processes for wireless chip design. Not only that, the current Virtuoso has integrated technology from partners such as Agilent, CoWare, Helic, and Mathworks, which greatly enhances RF design capabilities. Using this new technology can reduce design iterations and shorten time to market. Its AMS tool can realize top-down, digital/analog mixed circuit design; Composer tool can conveniently carry on input and management of circuit design; Spectre/SpectreRF simulator has high precision, suitable for circuit design with different characteristics; Layout tool includes Layout, Cross Reference, Routing, Layout Verification, Parameter Extraction, etc. In addition, Virtuoso can perform reliable post simulation and yield control.

Virtuoso-based behavioral simulation and system planning

Whether the design of the radio frequency transceiver system can be successful and whether the allocation of the module indicators is reasonable and feasible depends on the modeling and calculation of the behavior of the system before the specific circuit design, that is, the so-called behavior simulation. This is also a key step in the top-down design pattern. Cadence's built-in Verilog-A and VHDL emulators, as well as simulation methods with mixed input modes, offer this possibility. Moreover, Cadence software provides a large number of behavioral models free of charge for use. For RF system design, all that needs to be done is to call and set the expected index requirements of each module, and the system's behavior characteristics can be quickly obtained through simulation. According to the requirements, the indexes of each module can be easily modified and re-simulated until the system's behavior meets the requirements. Take the receiver as an example, the receiving system is shown in Figure 2. The specification of each module is very specific, such as input and output impedance, gain, isolation, noise figure NF, linearity IP3, DC offset IP2, and so on. After the simulation is completed, the task of allocating each module is also completed at the same time.

After each module is implemented with specific circuits, the corresponding design modules can be replaced one by one to perform system simulation. It can be seen whether each module meets the needs of the system and then evaluates the impact of each actual module on system performance.

Virtuoso Spectre/SpectreRF Based Circuit Modules

Simulation design

Based on the behavior simulation results and the index allocation results described above, the system module design task can be divided and the design simulation can be performed for each unit block.

LNA

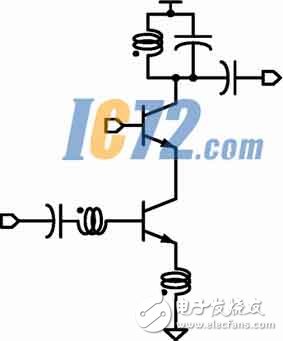

The LNA is the most active part of the RF receiver and determines the noise performance of the system. Its requirements are mainly to have the lowest possible NF and sufficient power gain, good input matching, followed by high linearity and isolation. Its circuit is shown in Figure 3. NF analysis can be performed using Spectre's SP analysis or SpectreRF's PSS+Pnoise analysis. The NFmin result can also be used to select the size of the transistor so that the optimal source impedance meets the minimum noise requirement.

Figure 2 LNA circuit schematic

Mixer

The mixer is the core of the transceiver. Since the frequency conversion work is completed, the main simulation method needs to use the SpectreRF simulator. The gain, NF, etc. of the mixer are related to the input and output, but the input and output work in different frequency bands. It is often necessary to perform other analysis on the basis of the PSS analysis to obtain correct results, such as PSP, Pnoise, and PAC. The structure of the mixer is a typical double-balanced Gilbert.

VGA

Baseband VGA has low requirements for noise because of its low frequency and large gain. It is mainly required for linearity, gain, and other indicators. SpectreRF's PSS scan can easily scan the module's input and automatically scan the curve. Extended, directly indicating the intersection point and magnitude of linearity P1dB and IIP3, very convenient and intuitive. This method is more flexible and efficient than the traditional two tone test. The simulation of IIP3 index of VGA in different gain states only needs to write the control into a variable and scan the variable value in the ADE environment to complete. The results obtained can be easily compared and analyzed. Adjust to get the ideal VGA circuit. It is even possible to save various settings under the ADE as ocean script files. With the script running automatically, Cadence can automatically complete simulations and save data results as long as various simulation tasks are scheduled in advance. After comparing and analyzing the data, you can learn about the performance of the circuit and use it as a guide for gradual improvement. Then you can obtain a circuit module that meets the needs of the system.

PLL module

The simulation of PLL modules is a challenging task. PLL itself is a digital/analog mixed module, but each module is usually designed in an analog way. The simulation of the PLL includes the testing of hundreds of metrics that use almost all of the Spectre and SpectreRF simulation tools. Taking the simulation of VCO and CP as an example, the non-linear VCO operation characteristics determine that its noise calculation cannot be performed in a small signal manner, and the PSS+Pnoise method can accurately simulate the VCO phase noise performance. The VCO frequency tuning gain Kvco can be obtained by scanning.

The charge pump output current characteristic is a commonly used measure of CP performance. The CP determines the gain and in-band noise performance of the PLL loop. The constant current and matching characteristics of the current source of the CP in different states can also be easily obtained by scanning.

The above is the circuit design simulation process for several typical unit modules of RF receivers. The simulation of each unit block of the system can be carried out at the same time. The completed module can be substituted into the behavior system at any time to verify the design results. After repeated modifications and verifications several times, the receiving system that meets the requirements can be finally obtained.

Temperature analysis

To ensure the reliability and yield of the final system design, a critical step is to perform temperature and extreme conditions analysis in the design of each cell block. These functions can be performed in Cadence Virtuoso by setting different simulation temperatures, through the simulation model's Corner settings, and directly using the Monte Carlo simulation tools provided.

Overall circuit simulation of RF transceiver system

After each module circuit is designed and verified separately, all modules can be connected into a system, and a complete chip system is formed by adding PAD, ESD, etc., as shown in FIG. 4 . The system is stimulated and tested for simulation. As shown in Figure 5, the entire system circuit can be simulated. If the hardware resources used in the simulation calculation are large enough, the system can be directly analyzed by tran, SP, PSS, and PSP, Pnoise, PAC, etc. to obtain the performance of the entire chip. If the resources are insufficient, you can consider grouping and block-by-function emulation of the system. Because the separated blocks are relatively independent, the characteristics of the overall system have little difference with the block simulation.

Layout design and post-simulation

The layout design of each module can be started on the basis of the design specifications of each module to meet its own and system requirements, as shown in FIG. 6 . First of all, using Layout-XL's component call function can be directly transferred from the schematic to the layout components, and a rough layout of each module is mainly arranged with the connection ports of other modules and the pre-layout of some important components. Then the prelayout of all modules is transferred from the system for overall layout considerations. Utilizing the hierarchical management and operational features of the Virtuoso Layout tool, it is possible to systematically consider the placement of each module and its interface with other modules.

Figure 3 Single chip RF transceiver chip layout design

After the system layout, the boundary conditions are assigned to each module. Observe its boundary conventions during the individual layout of the module. After the layout has reached a certain stage, it can be transferred to the system layout for inspection, making necessary adjustments at any time to meet the specific conditions of each module.

The layout drawing process can make full use of the powerful features of the Virtuoso layout tools. For example, full use of shortcut keys can make the layout design smooth and efficient; using Layout-XL cross-reference can always find the wrong connection or short circuit caused by inadvertent use; DRD's real-time rule checks can avoid most layouts that violate design rules.

The rule check of the layout can use Virtuoso's Diva tool. DRC, LVS, Extract and other tasks can all be completed in its friendly interface. For the feature that the number of RF circuit layout components is not large, it is appropriate to use Diva to complete most of the work. If you want to further improve the accuracy of layout extraction and post-simulation, consider using the Assura tool.

Conclusion

This article discusses in detail the design process of a monolithic RF transceiver integrated circuit based on the Cadence Virtuoso design platform. The entire design step from the top down, from the system to the module, and from the front end to the back end using Virtuoso tools was discussed until a complete RF chip was implemented. It can be seen that the Virtuoso platform tools play an important role in all stages of IC design.

The Virtuoso tool used in the single-chip radio frequency chip design described in this article is just the most commonly used tool in the Virtuoso family. It depends on their powerful functions to complete the complex RF system design and is a cost-effective solution. If combined with Virtuoso's AMS, UltraSim, VoltageStorm, ElectronStorm and other tools, will make the design more efficient and more accurate design.

E-mel kepada pembekal ini

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.