Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Select Language

This article guides reading

I believe that everyone will encounter such a situation, when you are knocking on a document or a piece of code, you have a blackout, I rub, ..., my code ..., my drawings ... ..., I just wrote the article .... However, similar situations may be encountered in embedded systems, which often result in the loss of embedded system data, programs, and failure to work or even damage the storage system. For the embedded system of the core board, the data is not lost under the abnormal power-down situation, and the stability is fundamental. Based on the CAT706, this article describes a method that can detect an abnormal power loss and use the small amount of power stored in the capacitor to save data, prevent memory corruption, and lose data.I. Overview

First quoted a WeChat article "The boss said: You go to change jobs, I go to jump! A disaster caused by the SD card"

In the first half of last year, our company undertook an elevator advertising display project of a large advertising company. This product used Freescale's IMX6 series chip as the main control CPU, with the media man-machine touch interaction, media placement, remote upgrade, video Monitoring and other functions. One of the important functions is the monitoring and saving function. Because the customer's offer is low, we naturally choose the SD card as the storage medium for the recording data.

Unexpectedly, the disaster fell after half a year. The 10K machine shipped six months ago has a 10% damage rate every month. 90% of the damaged machines are damaged by the SD card! The customer not only requires us to compensate for the loss of the SD card, extend the warranty period, but also threatens to terminate the cooperation within one month. The customer is the only big customer of the boss, and losing this customer is not far away from us. The boss even put down a lie: If you don't solve it within a month, you jump and I jump.

After careful inspection, the reason for the SD card's damage was caused by powering the device.

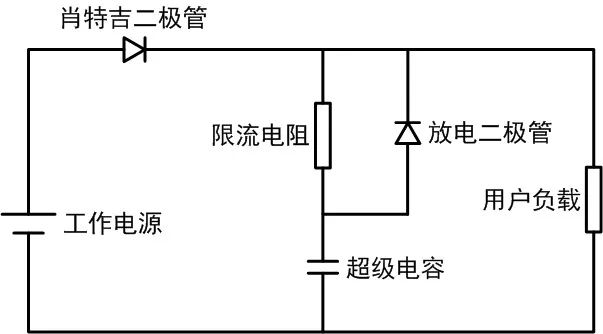

So we adopted the following scheme. The core of the solution is the power-failure detection circuit and the super capacitor continuous power supply circuit. The power-fail detection circuit is a comparatively complex comparison circuit built with an op amp, which is not shown here due to its complexity. Fig. 1 is the charging and discharging circuit of the supercapacitor. The addition of this circuit can keep the power off for 2 seconds and make the CPU perform the protection processing after power-off.

Figure 1 Super capacitor charging and discharging circuit

The above-mentioned case outcome method is to use an operational amplifier to build a power-failure detection circuit which is complicated and prone to problems. Here, we recommend a highly integrated power-failure detection circuit.

Second, function introduction:

Figure 2 shows the internal block diagram of the CAT706 chip. The CAT706 integrates multiple functions and is powerful and easy to use. This time, it only focuses on its internal power-failure detection function.

Figure 2 internal functional block diagram

Because the internal block diagram is very simple, it can be easily analyzed that the following four conditions can cause the microcontroller to reset or interrupt:

VCC power supply does not meet the requirements can lead to RESET reset output;

MR pin can manually reset RESET output;

Watchdog WDI does not feed the dog in time can cause WDO to reset the output;

The power down detection input PFI can cause the PFO interrupt output.

The following four functions are applied to the embedded system as follows:

It can ensure that the VCC supply is stable when the SCM is working, and when the output is unstable, the output can be reset to ensure the stable operation of the system.

Can manually control the microcontroller to reset the operation;

Watchdog real-time monitoring system to prevent the system from crashing;

Timely monitoring of the power supply system for power down allows the system to process data quickly.

This article focuses on its fourth point of protection against accidental power loss protection.

Third, typical application

PFI is equivalent to the positive input of a voltage comparator. If PFI voltage is higher than 1.25V then PFO will output high level. If PFI voltage is lower than 1.25V, PFO will output low level. In this way, the front-end high voltage can be divided and accessed through PFI as an input, so that the front-end power-off situation can be detected in advance.

Figure 3 shows a typical CAT706 application circuit and timing diagram. The schematic is relatively simple and easy to understand, and draws the theoretical waveforms of each part after power-off and power-up.

Under normal circumstances, the power supply of the system is stepped down from the front-end utility to a relatively high DC voltage (such as 12V), and then stepped down to the voltage required by the system (such as 5V/3.3V). Figure 3 shows the brownout detection circuit for the 12V DC voltage at the front end.

Figure 3 Typical Application Circuits and Timing Diagrams

When the 12V is powered on, the 5V output will charge the large capacitor. In the figure, a resistor is connected in series to limit the current. When the power is off, the capacitor's power will be discharged directly to the back-end load through the Schottky diode next to it.

Since there is a time difference between the 12V power-down and 5V/3.3V power-off completion, it is possible to detect the power-off condition of 12V in advance to make the microcontroller enter the Interrupt and take a series of countermeasures against power failure, and before the 5V/3.3V power-down is completed. Completion of operation, as shown in the time T, and this period of time T is related to the size of the red circle capacitance in the figure, the longer the capacitance is, the longer the time T (if necessary, consider using a Farah capacitor); and detect the power-down The closer the signal is to the front end of the mains, the better.

In order to increase the maintenance time T after power-off, not only the value of the storage capacitor can be increased to achieve the purpose, but also the brownout detection signal can be moved to the front end, for example, the 220V mains power supply or the front end that detects brownout can be moved to the front end. There is also a period of time between the high voltage and the 12V power-off when the mains power is off, so that the maintenance time T after the power-off can be increased indirectly.

Shown in Figure 4 is a power-down detection circuit that detects the front-end voltage. The power-down signal is processed in advance to increase the voltage maintenance time after power-off.

Figure 4 front-end power-failure detection circuit

With the placement of the Farad capacitor as shown in Figure 3, it is known that the voltage on the capacitor will gradually decrease as the voltage after power-down is maintained, which may affect the operation of the back-end system. For this purpose, the large-capacity charge/discharge circuit can be moved to the high-voltage part of the front end, or the step-down circuit can be divided into two or three buck connections, so that only the place where the large capacitor is placed can be shifted toward the front end. It can be ensured that the operating voltage of the main system remains stable during the period when the power failure is maintained. As shown in Figure 4, the placement of large capacitors is changed.

Fourth, the actual analysis

For the calculation of the CAT706 principle and the calculation of the actual effect waveform in the previous section, we made the following hardware circuit construction. The hardware circuit is constructed for Figure 3. As shown in Figure 5, the hardware is constructed using a hole board to test the actual input supply voltage waveform, output voltage waveform, and waveforms of the PFO and RST pins.

Figure 5 physical map

As shown in FIG. 6, waveform 1 is the input 12V voltage waveform, waveform 2 is the output 5V voltage waveform, waveform 3 is the reset pin voltage waveform, and waveform 4 is the PFO pin voltage waveform. In the figure, the output was discharged at a constant current of 10 mA.

Figure 6 Test waveforms

When the input 12V rises, the DCDC power supply will start to output 5V immediately. At the same time, if 12V rise, if its partial voltage value is greater than the input threshold of PFI, PFO will immediately output high level. The reset pin detects 5V voltage normally. After a while, the system will be reset and the system will start working.

When the input 12V drops unexpectedly, the PFO will immediately output a low level when the voltage on the PFI pin is lower than the threshold. This PFO low interrupts the system master and informs the system that the unexpected power failure should be immediately stored. Data is processed to prevent data loss. The test waveform in the figure is a constant current load simulation test effect of 10mA. From the figure, it can be seen that there is a 244ms processing time from the detection of an unexpected power-off to the stop of the system reset. This time has a great relationship with the capacitance of the DCDC output. The greater the capacitance value, the longer the data processing time is. The figure shows the time when the capacitance value of 2200 μF and the load current of 10 mA are constant. When the power down is detected in the actual processing, the main control should immediately cut off the unnecessary power consumption peripherals such as the LCD screen, and only maintain the power supply of the main control part.

E-mel kepada pembekal ini

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.